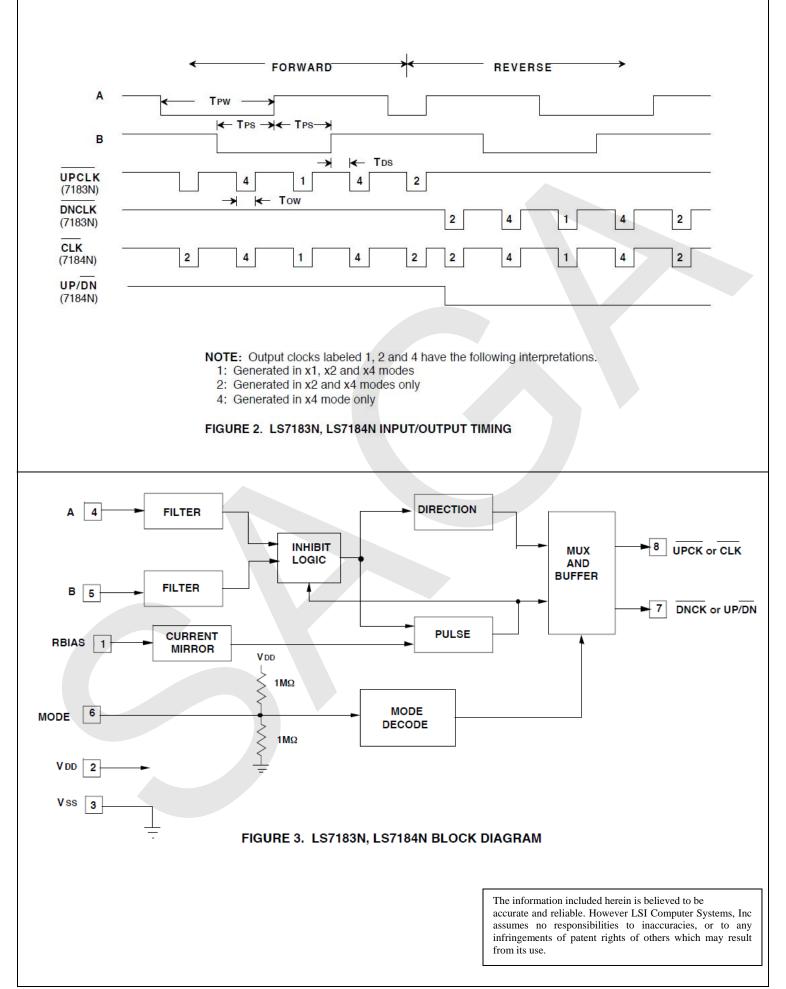

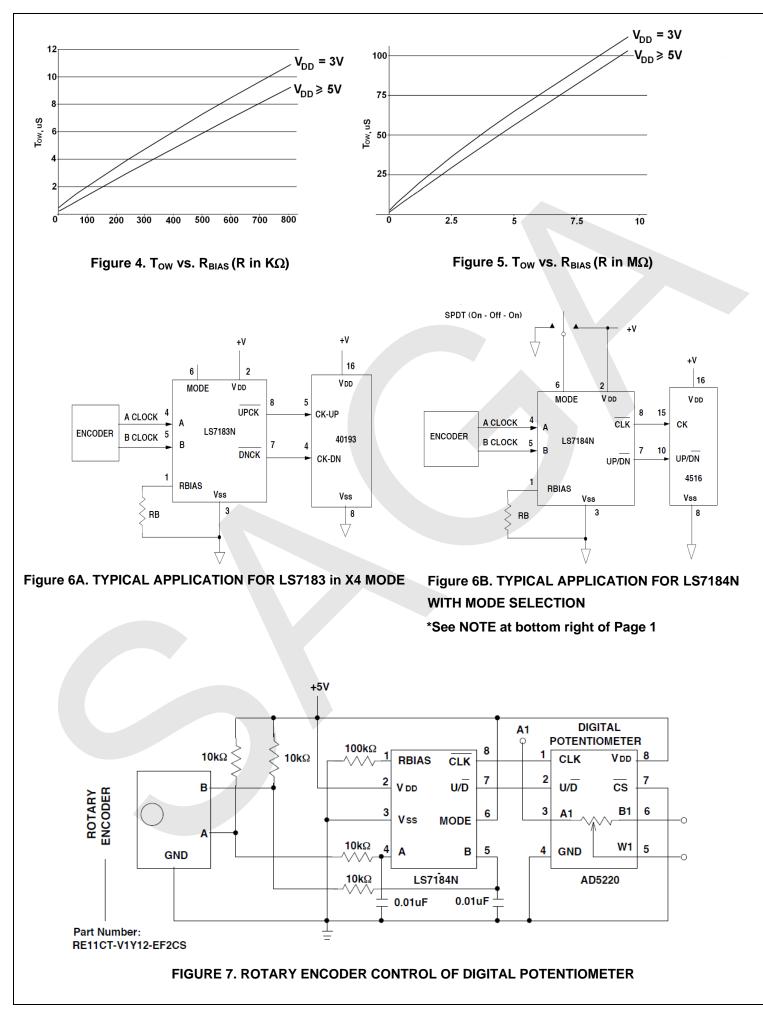

Quadrature Clock inputs A and B. Directional output pulses are generated from the A and B clocks according to Fig. 2. A and B inputs have built-in immunity for noise signals less than 50ns duration (Validation delay, TvD). The A and B inputs are inhibited during the occurrence of a directional output clock (UPCK or DNCK), so that spurious clocks resulting from encoder dither are rejected.

## MODE (Pin 6)

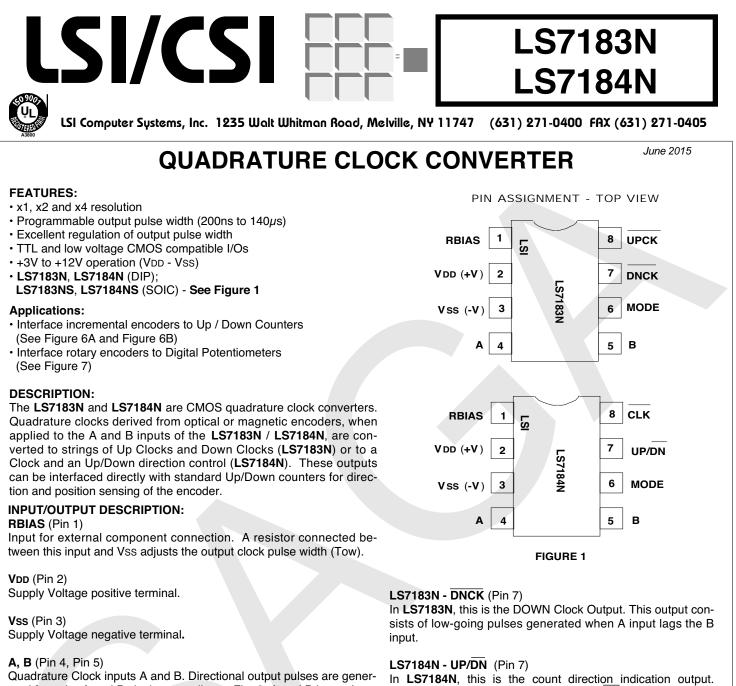

MODE is a 3-state input to select resolution x1, x2 or x4. The input quadrature clock rate is multiplied by factors of 1, 2 and 4 in x1, x2 and x4 mode, respectively, in producing the output UP/ $\overline{DN}$  clocks (See Fig. 2). x1, x2 and x4 modes selected by the MODE input logic levels are as follows:

## the B input, UP/DN output goes low, indicating that the count direction is DOWN.

## LS7183N - UPCK (Pin 8)

In **LS7183N**, this is the UP Clock output. This output consists of low-going pulses generated when A input leads the B input.

When A input leads the B input, the UP/DN output goes high

indicating that the count direction is UP. When A input lags

## LS7184N - CLK (Pin 8)

In **LS7184N**, this is the combined UP Clock and DOWN Clock output. The count direction at any instant is indicated by the UP/DN output (Pin 7).

**NOTE**: For the **LS7184N**, the timing of  $\overline{\text{CLK}}$  and  $\text{UP}/\overline{\text{DN}}$  requires that the counter interfacing with **LS7184N** counts on the rising edge of the  $\overline{\text{CLK}}$  pulses.

| ABSOLUTE MAXIMUM RAT     | INGS:               |                                  |                  |                                        |           |                                                                                                     |

|--------------------------|---------------------|----------------------------------|------------------|----------------------------------------|-----------|-----------------------------------------------------------------------------------------------------|

| PARAMETER                | SYMBOL              |                                  | VALUE            |                                        | UNITS     |                                                                                                     |

| DC Supply Voltage        | $V_{DD}$ - $V_{SS}$ |                                  | 16               |                                        | V         |                                                                                                     |

| Voltage at any input     | V <sub>IN</sub>     | V <sub>SS</sub> -                | -0.3 to $V_{DE}$ | +0.3                                   | V         |                                                                                                     |

| Operating temperature    | T <sub>A</sub>      |                                  | -20 to +85       | 5                                      | ٥C        |                                                                                                     |

| Storage temperature      | T <sub>STG</sub>    |                                  | -55 to 150       | )                                      | ٥C        |                                                                                                     |

| DC ELECTRICAL CHARACT    | ERISTICS:           | (Unless otherw                   | vise specif      | ied VDD=3V to 2                        | 12V and T | A=-20°C to +85°C)                                                                                   |

| PARAMETER                | SYMBOL              | MIN                              | ТҮР              | MAX                                    | UNITS     | CONDITION                                                                                           |

| Supply Voltage           | $V_{DD}$            | 3                                | -                | 12                                     | V         |                                                                                                     |

| Supply Current           | I <sub>DD</sub>     | -                                | 1.5              | 1.65                                   | mA        | $V_{\text{DD}}\text{=}12\text{V},$ all input frequencies=0 Hz and $R_{\text{BIAS}}\text{=}2M\Omega$ |

| Mode input:              |                     |                                  |                  |                                        |           |                                                                                                     |

| Logic 0                  | V <sub>ml</sub>     | -                                | -                | 0.5                                    | V         |                                                                                                     |

| Logic 1                  | V <sub>mh</sub>     | V <sub>DD</sub> - 0.5            | -                | -                                      | V         |                                                                                                     |

| Logic Float              | V <sub>mf</sub>     | (V <sub>DD</sub> /2) - 0.5       | $V_{DD}/2$       | (V <sub>DD</sub> /2) + 0.5             | V         | -                                                                                                   |

| Logic 0 Input Current    | I <sub>ml</sub>     | -                                | 2.2              | 4.2                                    | μA        | $V_{DD} = 3V$                                                                                       |

|                          | I <sub>ml</sub>     | -                                | 3.5              | 6.9                                    | μΑ        | $V_{DD} = 5V$                                                                                       |

|                          | I <sub>ml</sub>     | -                                | 8.3              | 16.2                                   | μA        | $V_{DD} = 12V$                                                                                      |

| Logic 1 Input Current    | I <sub>mh</sub>     | -                                | -2               | -9.8                                   | μA        | $V_{DD} = 3V$                                                                                       |

|                          | I <sub>mh</sub>     | -                                | -3.4             | -6.6                                   | μΑ        | $V_{DD} = 5V$                                                                                       |

|                          | I <sub>mh</sub>     | -                                | -8.2             | -16                                    | μA        | $V_{DD} = 12V$                                                                                      |

| A,B INPUTS:              |                     |                                  |                  |                                        | P# 1      | 55                                                                                                  |

| Logic 0                  | V <sub>ABI</sub>    | -                                |                  | 0.25V <sub>DD</sub>                    | V         |                                                                                                     |

| Logic 1                  | V <sub>ABh</sub>    | 0.7V <sub>DD</sub>               | -                | -                                      | V         |                                                                                                     |

| Input Current            | I <sub>ABlk</sub>   | -                                | 0                | 10                                     | nA        |                                                                                                     |

| RBIAS INPUT:             | ADIK                |                                  | -                |                                        |           |                                                                                                     |

| External Resistor        | R <sub>B</sub>      | 2K                               | -                | 10M                                    | Ω         | -                                                                                                   |

| ALL OUTPUTS:             | Б                   |                                  |                  |                                        |           |                                                                                                     |

| Sink Current             | I <sub>ol</sub>     |                                  | -3.4             |                                        | mA        | $V_{O} = 0.5V, V_{DD} = 3V$                                                                         |

|                          | I <sub>ol</sub>     | -                                | -4.8             |                                        | mA        | $V_0 = 0.5V$ , $V_{DD} = 5V$                                                                        |

|                          | I <sub>ol</sub>     |                                  | -7.2             |                                        | mA        | $V_0 = 0.5V, V_{DD} = 12V$                                                                          |

| Source Current           | I <sub>oh</sub>     | _                                | 1.7              | <u>.</u>                               | mA        | $V_{\rm O} = 2.5V, V_{\rm DD} = 3V$                                                                 |

|                          | I <sub>oh</sub>     | _                                | 2.2              | -                                      | mA        | $V_{O} = 4.5V, V_{DD} = 5V$                                                                         |

|                          | I <sub>oh</sub>     |                                  | 3.1              | -                                      | mA        | $V_0 = 11.5V, V_{DD} = 12V$                                                                         |

| TRANSIENT CHARACTERIS    |                     | PC to +85°C)                     | 5.1              |                                        | 111/ \    |                                                                                                     |

| PARAMETER                | SYMBOL              | MIN                              | ТҮР              | МАХ                                    | UNITS     | CONDITION                                                                                           |

| Output Clock Pulse Width | T <sub>ow</sub>     | 540                              |                  |                                        | ns        | $V_{DD} = 3V$                                                                                       |

|                          | T <sub>ow</sub>     | 225                              |                  |                                        | ns        | $V_{DD} = 5V$                                                                                       |

|                          | T <sub>ow</sub>     | 112                              |                  |                                        | ns        | $V_{DD} = 12V$                                                                                      |

| A,B INPUTS:              | 010                 |                                  |                  |                                        |           |                                                                                                     |

| Validation Delay         | T <sub>VD</sub>     | -                                | 450              | -                                      |           | $V_{DD} = 3V$                                                                                       |

| j                        | T <sub>VD</sub>     |                                  | 200              | -                                      |           | $V_{DD} = 5V$                                                                                       |

|                          | T <sub>VD</sub>     | -                                | 90               | -                                      |           | $V_{DD} = 12V$                                                                                      |

| Phase Delay              | T <sub>PS</sub>     | T <sub>VD</sub> +T <sub>OW</sub> |                  | ×                                      | S         | -                                                                                                   |

| Pulse Width              | T <sub>PW</sub>     | 2T <sub>PS</sub>                 | -                | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | S         | _                                                                                                   |

| Frequency                | f <sub>A,B</sub>    |                                  |                  | 1/(2T <sub>PW</sub> )                  | Hz        | _                                                                                                   |

| Input to output Delay    | T <sub>DS</sub>     | _                                | 490              | 565                                    | ns        | V <sub>DD</sub> = 3V                                                                                |

| mpar to output Delay     |                     | -                                |                  |                                        |           |                                                                                                     |

|                          | T <sub>DS</sub>     | -                                | 220              | 345                                    | ns        | $V_{DD} = 5V$                                                                                       |

|                          | T <sub>DS</sub>     | -                                | 125              | 135                                    | ns        | $V_{DD} = 12V$                                                                                      |

7183N/7184N-062315-2